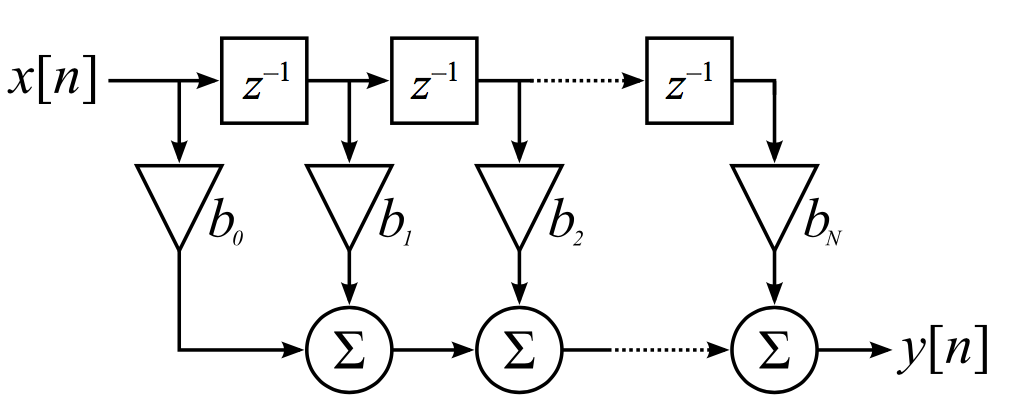

Transposed FIR Filter where N is the number of filter taps-1 ie. Modify the file VHDLfir_tbvhdl modifying the path for data io.

4 Taps Fir Filter Iv Use Cases Download Scientific Diagram

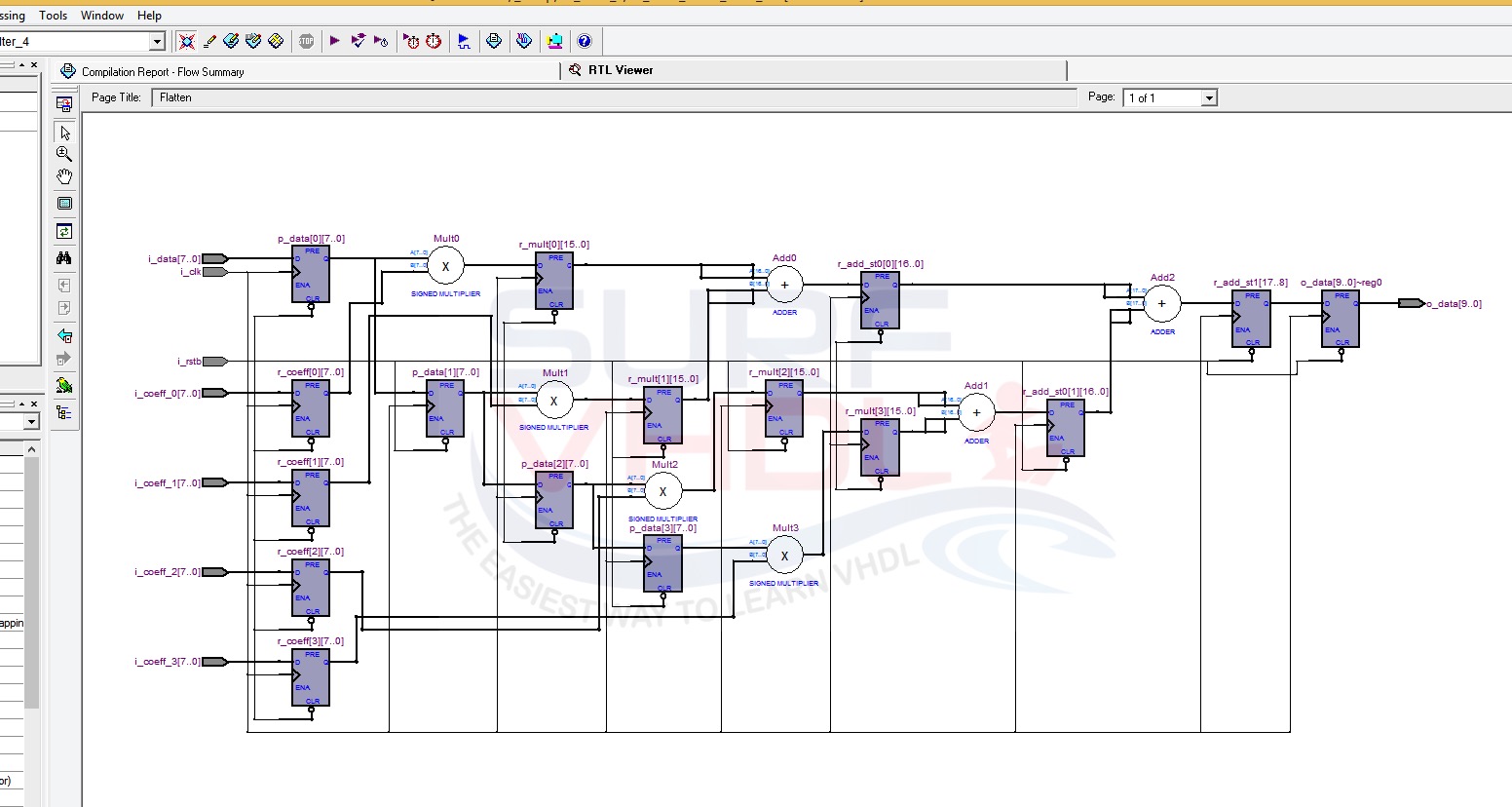

RTL-VHDL-Code Block diagram Algorithm High-Level System Diagram Context of the design Inputs and Outputs Throughputrates Algorithmic requirementsy k bi x k i N Algorithm Description Mathematical Description i 0 Performance Criteria x k y k.

. Sample ECG inputs are provided in inputtxt files the VHDL filter code reads those ECG files apply digital filtering and write the results into outputtxt files for verification. You can implement this quite easily in VHDL. Filter Design HDL Coder generates synthesizable portable VHDL and Verilog code for implementing fixed-point filters designed with MATLAB on FPGAs or ASICs.

Well use a 32-tap FIR filter as an example. Fir Filter Verilog Code Xilinx another introduction to fpgas hackaday. Logic Home Code Download FIR Filter top level file.

The simplest low pass FIR filter you can try is y n x n x n-1. According to the formula you need the current and previous ADC samples in order to get the appropriate output. 1 Points Download Earn points.

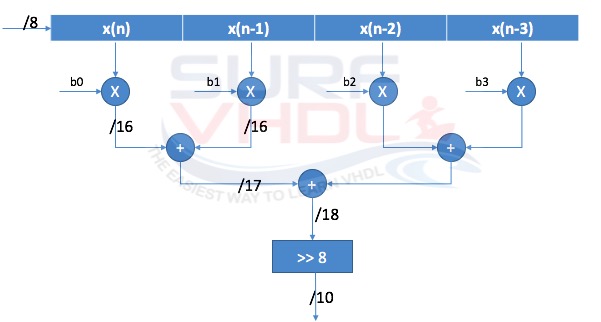

May 8th 2018 - DESIGN OF 30 TAP FIR FILTER USING VHDL code 12 Table 3 Co IIR filters or infinite impulse response filters 17 design of fir filter using verilog hdl copy scribd may 10th 2018 - this is in contrast to infinite impulse response iir filters design of fir filter using. The VHDL code implements a low pass FIR filter with 4 taps 8-bit input 8-bit coefficient. This is a 4 tap filter.

Since the design of FIR digital filters is non-analytic we aim at ideal zero-phase magnitude. VHDL VHSIC hardware description language. Video Lecture on an FPGA-Implementation of an FIR-Filter 2 of 4Project Homepagehttpwwwh-brsdefpga-vision-labSource Code available athttpsgithub.

For writing the code in Verilog I have referred to the paper VHDL generation of optimized FIR filters. Peer reviewed journal ijera com. It automatically creates VHDL and Verilog test benches for simulating testing and verifying the generated code.

That means the order of the filter is 4 and so it has 4 coefficients. Explore the Generated VHDL Code Get familiar with the generated VHDL code by opening and browsing through the file basicfirvhd in an ASCII or HDL simulator editor. For a FIR filter applies impulse step ramp chirp and white noise stimulus types.

Dsp stm32 sound-processing fir-filter stm32h7 fir-filters multicore-programming. Reconfigurable fir filter vhdl code. Below is a very simple block diagram of the hardware you want to implement.

Timescale 1ns 1ps module FIR input clk. VHDL VHSIC hardware description language. Typesvhd 18 KB Features VHDL source code of a FIR Filter component Configurable size of data input Configurable size of coefficient inputs Configurable number of taps Introduction This details a FIR Filter circuit written in VHDL for.

You can say I have coded the exact block diagram available in the paper Figure 2. When you have finished generating code click Close to close the Generate HDL dialog box. This is a 4 tap filter.

Logic for simple 15-tap FIR to be written in Verilog or VHDL Notice how the valid and ready signals set the enable value for the input circular buffer and the multiply stage of the FIR and each of the registers that the data or coefficients pass through are declared as signed. For writing the code in VHDL I have referred to the paper VHDL generation of optimized FIR filters. FIR module Verilog code.

The algorithm runs in parallel on both cores and this helps users to achieve high sampling frequencies or higher FIR filter order. FIR Filter Where to start. Figure 2 Transposed Form Of FIR Filter 09 Figure 3 Top level schema of the FIR filter 11 Figure 4 Xilinx 142 report of the filter design 13 Figure 5 VHDL Top level RTL Schema1 14 Figure 6 VHDL Top level RTL Schema2 14 Figure 7 Xilinx 142 full schematic of FIR order 30 filter.

A low pass fir filter for ecg denoising in vhdl. Run the testbench on ModelSim. VHDL code for the FIR filter is fully presented.

STM32H7 Multicore FIR is a finite impulse response filter implementation for a family of multicore processors from STM32 - family H7. Peer reviewed journal ijera com. Pynq python productivity for zynq community.

VHDL Finite Impulse Response FIR Filter Share Finite Impulse Response FIR Filter The VHDL code presented in this model will show you how to describe a typical reference model in VHDL. For a discussion of the advantages of reference models please refer to our Tips page. Very-high-speed integrated circuit is a hardware description language used in electronic design automation to.

The higher the value of N is the more complex the filter will be. The VHDL code for the FIR filter is simulated and verified by comparing the simulated results in Modelsim with the correct results generated from Matlab. Very-high-speed integrated circuit is a hardware description language used in electronic design automation to.

Create the lowpass filter design object then create the FIR Filter System object Hlp. An implementation of a FIR filter in particular using the transposed form. Source Code reconfigurable fir filter vhdl code.

Fir_filtervhd 33 KB Data Types must also be included in project. 15 Figure 8 Test bench simulation of 30 order FIR filter 16. Then transform it to create a FIR Filter System object with a highpass response Hhp.

Vhdl tutorial learn by example. Here below is reported the VHDL code for the FIR filter design of figure 2. You can say I have coded the exact block diagram available in the paper Figure 2.

LS approach to design linear phase Finite Impulse Response FIR filter. Check IOoutput_resultstxt for the result. IIR filter VHDL code.

This is an fir filter implementation code for a reconfigurable fir filter design coded in vhdl language. Fpga amp verilog design mohammad s sadri. We will generate VHDL code for the filter and show the two responses using the generated VHDL test bench.

In IOinput_vectorstxt put the input integer you want to test. That means the order of the filter is 4 and so it has 4 coefficients.

Digital Filter Fir Using Vhdl Forum For Electronics

Pdf Vhdl Generation Of Optimized Fir Filters Semantic Scholar

Fpga Fir Filter Circuit Architecture And Vhdl Design Youtube

Fpga Code Example For Fir Iir Filters In Vhdl Electrical Engineering Stack Exchange

A Low Pass Fir Filter For Ecg Denoising In Vhdl Fpga4student Com

How To Implement Fir Filter In Vhdl Surf Vhdl

0 comments

Post a Comment